|

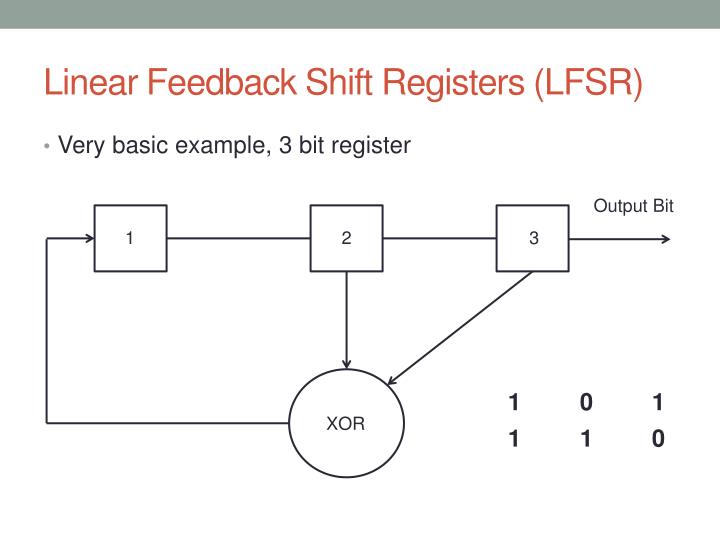

This work presents a three-step high-speed VLSI architecture for LFSR structures, this paper proposes improved three-step LFSR architecture with both higher hardware efficiency and speed. The serial input/output operation property of LFSR structure is a bottleneck in such systems and parallel LFSR architecture is thus required. MathPod 11.9K subscribers Subscribe 9.3K views 2 years ago Queuing Theory and Simulation This video is about Linear Feedback Shift Register Method For Random Sequnecs of Bits The basics of. The top layer is a linear feedback shift register (LFSR). Many current functions such as Scrambling, Convolutional Coding, CRC and even Cordic or Fast Fourier Transform can be derived as Linear Feedback Shift Registers (LFSR) In high-rate digital systems such as optical communication system, throughput of 1Gbps is usually desired. The second stage is a working stage and the algorithm produces a 32-bit word of output per loop. Linear Feedback Shift Register (LFSR) structures are widely used in digital signal processing and communication systems, such as BCH, CRC. Likewise, because the register has a finite number of possible states, it must eventually enter a repeating cycle Linear Feedback Shift Register (LFSR) is one of the algorithms for getting keys in the form the random number that keeps changing unpredictably in.

The initial value of the LFSR is called the seed, and because the operation of the register is deterministic, the stream of values produced by the register is completely determined by its current (or previous) state.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed